PCIe 8.0 Draft Unveiled: 1 TB/s, 0.5V Signaling, and Next-Gen Connectors

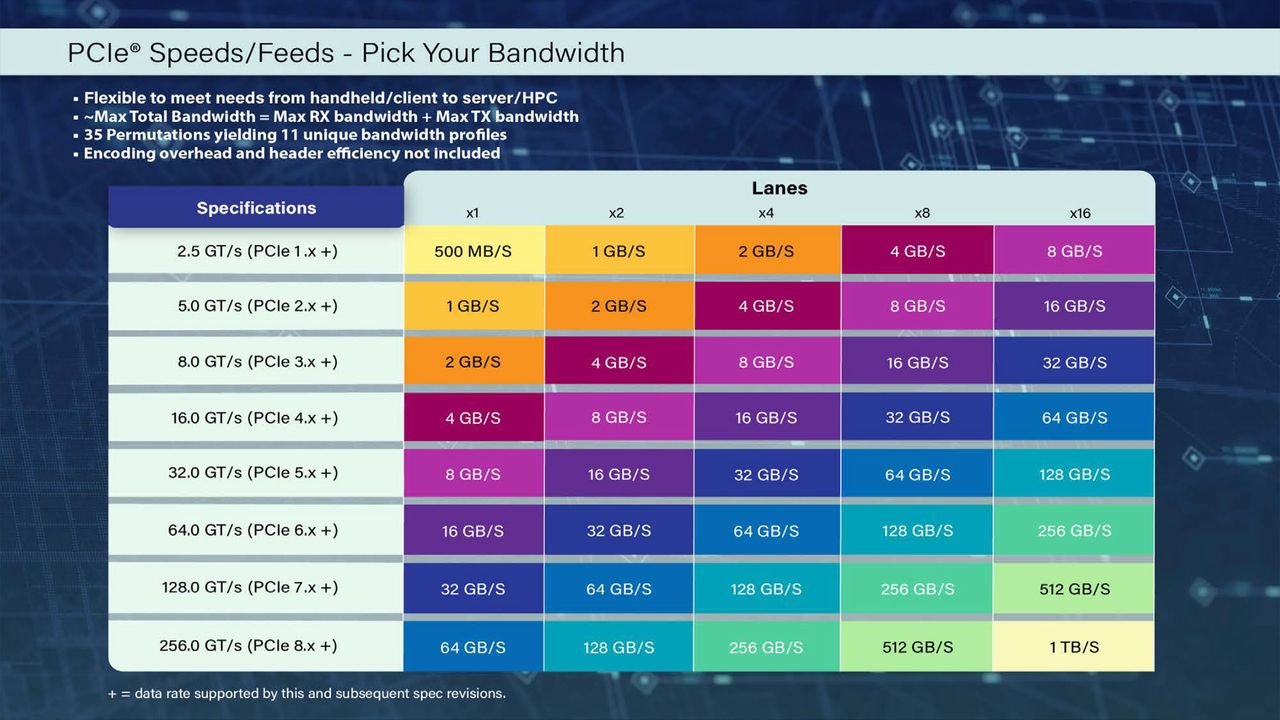

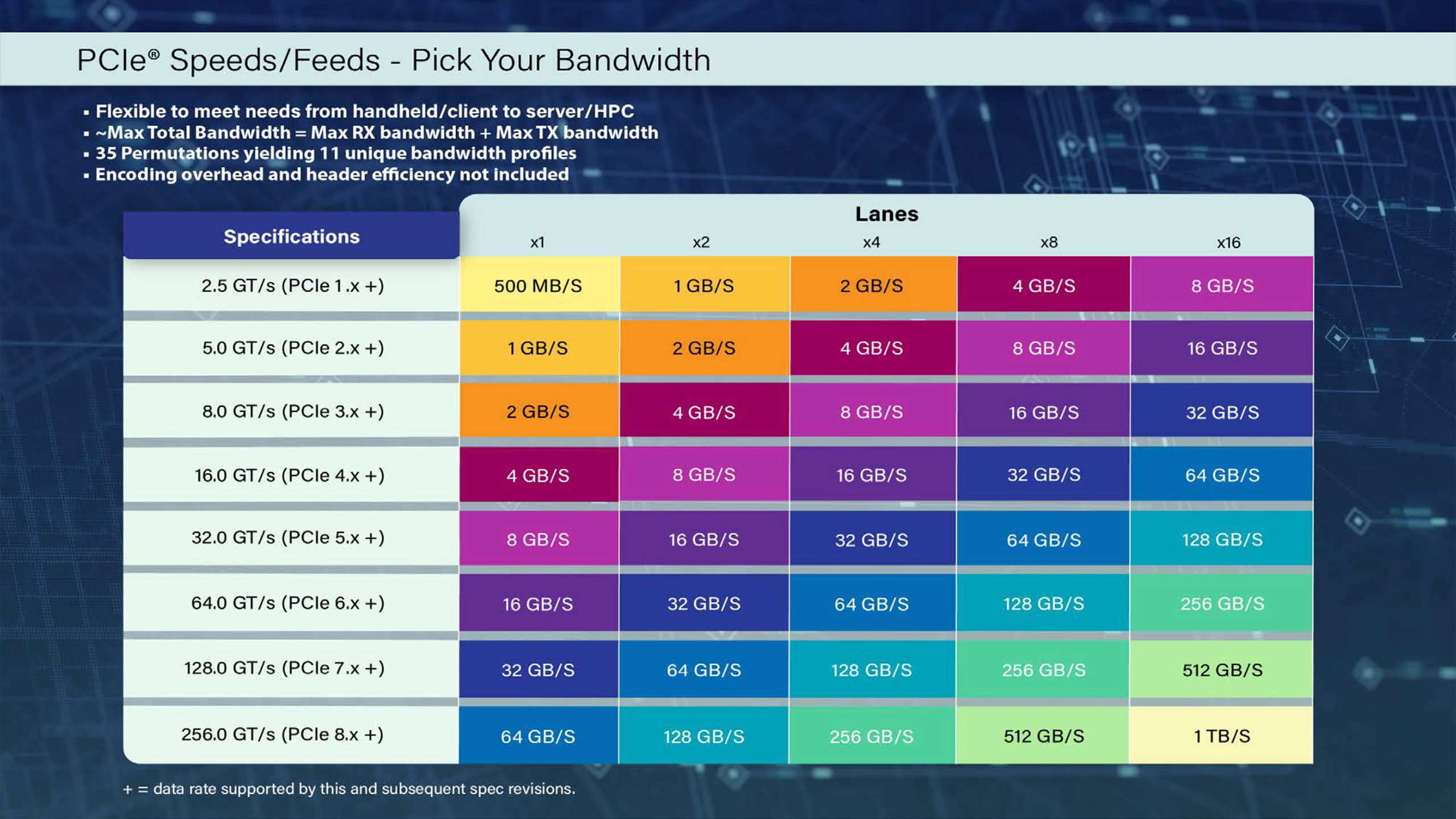

The PCI Special Interest Group (PCI-SIG) has released the first draft of the PCIe Gen 8 specification, setting the stage for a major leap in data center and high-performance computing connectivity. This next-generation standard promises a staggering 256 GT/s data transfer rate per lane, delivering up to 1 TB/s of aggregate bandwidth in a full x16 slot. Key innovations include a new connector design, a reduced voltage threshold of 0.5V for improved power efficiency, and full backward compatibility with previous PCIe generations. Final ratification is expected in 2028, giving the industry time to refine the technology.

What are the key performance specifications of PCIe 8.0?

PCIe 8.0 achieves a raw data rate of 256 GT/s per lane, which is double the 128 GT/s of PCIe 7.0. When configured with 16 lanes (x16), the bidirectional bandwidth reaches 1 TB/s (512 GB/s in each direction). This massive throughput is designed to meet the demands of emerging workloads like AI training, real-time analytics, and high-bandwidth storage. The signaling uses PAM4 modulation, similar to PCIe 6.0 and 7.0, but with improved equalization and error correction to maintain signal integrity at such high speeds. Additionally, the specification introduces a new connector technology capable of handling higher frequencies and reduced crosstalk, ensuring reliable performance in dense server environments.

What is the significance of the 0.5V voltage milestone in PCIe 8.0?

The 0.5V voltage threshold marks a major power efficiency improvement over previous generations. Earlier PCIe standards operated at higher voltages (e.g., 1.8V or 1.2V). By reducing the I/O voltage to 0.5V, PCIe 8.0 lowers power consumption per lane significantly, which is critical for large-scale data centers where thousands of lanes operate simultaneously. Lower voltage also reduces thermal output, allowing denser configurations without aggressive cooling. This milestone was achieved through advanced circuit designs and process technologies that enable reliable signaling at such low voltages while maintaining the 256 GT/s data rate.

Does PCIe 8.0 maintain backward compatibility with older devices?

Yes, PCIe 8.0 is fully backward compatible with all previous PCIe generations, including PCIe 7.0, 6.0, 5.0, 4.0, 3.0, 2.0, and 1.0. This means that existing PCIe devices (e.g., graphics cards, SSDs, network adapters) can be used in PCIe 8.0 slots, though they will operate at their native maximum speed. The backward compatibility is achieved through a negotiated link speed that falls back to the highest common supported rate between the host and device. For example, a PCIe 5.0 drive in a PCIe 8.0 slot will run at 32 GT/s. This design ensures a smooth transition for enterprise and consumer systems.

What new connector technology is being evaluated for PCIe 8.0?

PCI-SIG is evaluating a next-generation connector designed to handle the higher frequencies and signal integrity demands of PCIe 8.0. The new connector likely includes features like enhanced shielding, improved contact geometry, and reduced insertion loss to support 256 GT/s signaling. It may also incorporate a smaller pitch or different pin layout to accommodate more lanes in the same physical space. This connector is crucial because PCIe 8.0 operates at near-terahertz frequencies, making traditional connectors susceptible to crosstalk and attenuation. The final design will be finalized during the ratification process, with input from member companies.

What is the timeline for the final ratification of PCIe 8.0?

PCI-SIG expects final ratification of the PCIe 8.0 specification in 2028. The first draft was released in early 2025, kicking off a multi-year review and testing phase. During this period, member companies will conduct interoperability tests, refine the electrical parameters, and validate the new connector design. Historically, each PCIe generation takes about 4-5 years from draft to ratification (e.g., PCIe 7.0 draft in 2022, expected final in 2025). PCIe 8.0's timeline aligns with this pace, allowing the industry to develop compatible hardware and driving adoption across data centers and PCs.

What are the main use cases that will benefit from PCIe 8.0's bandwidth?

PCIe 8.0's 1 TB/s bandwidth is aimed at data-intensive applications that push current interconnects to their limits. Key use cases include:

- AI and machine learning: Training large language models and neural networks requires massive data transfers between GPUs, memory, and storage.

- High-performance computing (HPC): Scientific simulations and real-time analytics benefit from low-latency, high-throughput interconnects.

- NVMe storage: Next-gen SSDs with speeds of 100+ GB/s can fully utilize PCIe 8.0 lanes.

- Data center networking: SmartNICs and DPUs with 800 GbE or 1.6 TbE will rely on PCIe 8.0 to avoid bottlenecks.

These applications will drive adoption once ratified hardware becomes available after 2028.

Related Articles

- Man Pages Get a Major Overhaul: Developers Propose Cheat Sheets and Organized Options to End Confusion

- Cat5e Ethernet Cables Still Reign in Home Networks Despite Confusing Labels

- 10 Reasons to Grab the AdGuard VPN 5-Year Plan for $40

- Man Pages Get Makeover: New Examples for tcpdump and dig Simplify Network Diagnostics

- Why Skipping Motorola's Latest Razr for Last Year's Model Makes Sense

- Utah Enforces Landmark Law Making Websites Liable for VPN-Aided Age Verification Bypasses

- Rethinking Man Pages: How to Make Command Documentation More User-Friendly

- How to Discreetly Embed a Bluetooth Tracker in a Postcard for Mail Tracking